# Smart Photoflash Capacitor Charger with IGBT Driver

## **General Description**

The RT9591 is a highly integrated photoflash charging solution in digital and film cameras. It is targeted for applications that use either two AA batteries or a single lithium-ion battery.

The RT9591 integrates a constant current controller for charging high voltage photoflash capacitor quickly and efficiently, an IGBT driver for igniting flash tube, and a voltage detector. Only a few external components are used to reduce PCB space and cost.

RT9591 is available in VQFN-16L 3x3 package.

## **Ordering Information**

RT9591 🗖 📮

Package Type QV : VQFN-16L 3x3 (V-Type) ——Operating Temperature Range P : Pb Free with Commercial Standard

Note :

RichTek Pb-free products are :

- RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- Suitable for use in SnPb or Pb-free soldering processes.

- ▶100% matte tin (Sn) plating.

## **Marking Information**

For marking information, contact our sales representative directly or through a RichTek distributor located in your area, otherwise visit our website for detail.

### Features

- 1.8V to 6.5V Battery Input Voltage Range

- Charges Any Size Photoflash Capacitor

- Adjustable Input Current

- Uses Standard Transformers

- Adjustable Output Voltage

- Charge Complete Indicator

- Built-in IGBT Driver for IGBT Application

- Built-in Voltage Detector

- 16-Lead VQFN Package

- RoHS Compliant and 100% Lead (Pb)-Free

### **Applications**

- Digital Still Camera

- Film Camera Flash Unit

- Camera Phone Flash

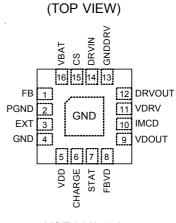

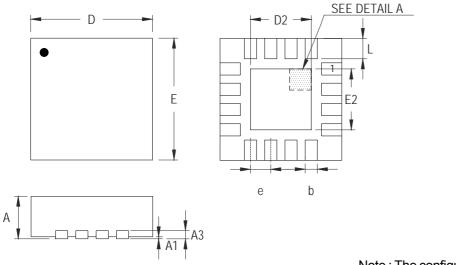

# **Pin Configurations**

VQFN-16L 3x3

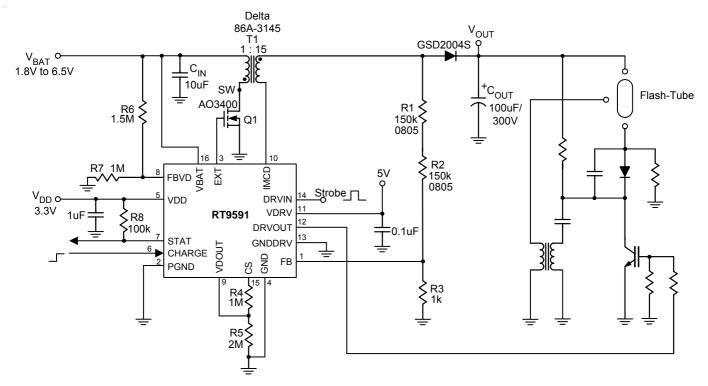

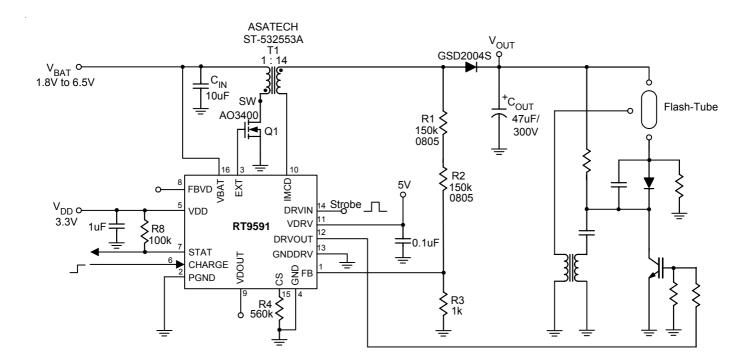

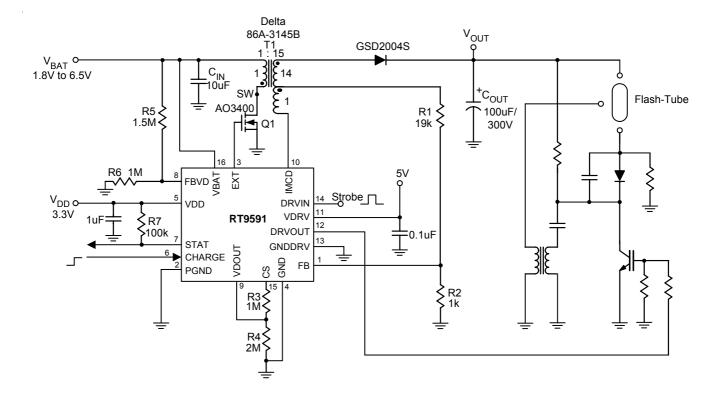

# **Typical Application Circuit**

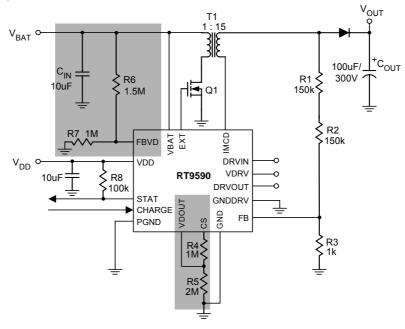

Figure 1. Photoflash Capacitor Charger Application

Figure 2. Photoflash Capacitor Charger Application for Low Charging Current

Figure 3. Photoflash Capacitor Charger Application with Center-Tap Transformer

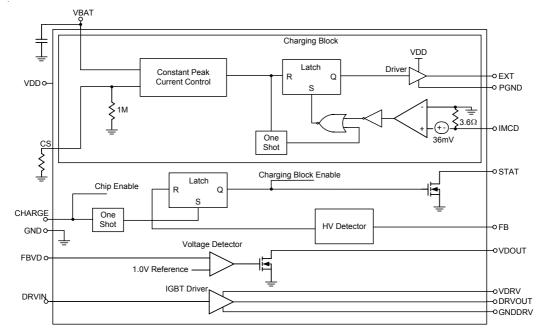

# **Function Block Diagram**

# **Functional Pin Description**

| Pin Number  | Pin Name | Pin Function                                                                                                                                                     |  |  |  |  |

|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 1           | FB       | Feedback Voltage Pin                                                                                                                                             |  |  |  |  |

| 2           | PGND     | ower Ground                                                                                                                                                      |  |  |  |  |

| 3           | EXT      | utput Pin for driving external NMOS on Flyback topology                                                                                                          |  |  |  |  |

| 4           | GND      | round                                                                                                                                                            |  |  |  |  |

| 5           | VDD      | Power Input Pin of RT9591                                                                                                                                        |  |  |  |  |

| 6           | CHARGE   | Charge Enable Pin, the charge function is executed when CHARGE pin is set from Low to High. And the RT9591 gets into Shutdown mode when CHARGE pin is set to Low |  |  |  |  |

| 7           | STAT     | Charge Status Output. Open Drain output. When target output voltage is reached, NMOS turns off. This pin needs a pull up resistor.                               |  |  |  |  |

| 8           | FBVD     | Voltage Detector Feedback Pin                                                                                                                                    |  |  |  |  |

| 9           | VDOUT    | Voltage Detector Output Pin, Open Drain output                                                                                                                   |  |  |  |  |

| 10          | IMCD     | Minimum Current Detection Pin                                                                                                                                    |  |  |  |  |

| 11          | VDRV     | IGBT Driver Power Pin                                                                                                                                            |  |  |  |  |

| 12          | DRVOUT   | IGBT Driver Output Pin                                                                                                                                           |  |  |  |  |

| 13          | GNDDRV   | IGBT Driver Ground pin                                                                                                                                           |  |  |  |  |

| 14          | DRVIN    | IGBT Driver Input Pin                                                                                                                                            |  |  |  |  |

| 15          | CS       | Input Current Setting Pin                                                                                                                                        |  |  |  |  |

| 16          | VBAT     | Battery Supply Voltage Input Pin                                                                                                                                 |  |  |  |  |

| Exposed Pad | GND      | Exposed pad should be soldered to PCB board and connected to GND                                                                                                 |  |  |  |  |

# Absolute Maximum Ratings(Note 1)

| <ul> <li>Supply Voltage, V<sub>DD</sub>, V<sub>BAT</sub>, V<sub>DRV</sub></li></ul> |       |

|-------------------------------------------------------------------------------------|-------|

| • IMCD                                                                              | ( ,   |

| Other I/O Pin Voltage                                                               |       |

| • Power Dissipation, $P_D @ T_A = 25^{\circ}C$                                      |       |

| VQFN-16L 3x3                                                                        | 1.67W |

| Package Thermal Resistance                                                          |       |

| VQFN-16L 3x3, $\theta_{JA}$                                                         |       |

| Junction Temperature                                                                | 150°C |

| • Lead Temperature (Soldering, 10 sec.)                                             | 260°C |

| Storage Temperature Range                                                           |       |

| ESD Susceptibility (Note 2)                                                         |       |

| HBM (Human Body Mode)                                                               | 2kV   |

| MM (Machine Mode)                                                                   | 200V  |

## **Electrical Characteristics**

(V<sub>DD</sub> = 3.3V, V<sub>VDRV</sub> = 3.3V, T<sub>A</sub> =  $25^{\circ}$ C, Unless Otherwise specification)

| Parameter                                               | Symbol                | Test Conditions                         | Min  | Тур  | Мах  | Units |

|---------------------------------------------------------|-----------------------|-----------------------------------------|------|------|------|-------|

| V <sub>DD</sub> Operating Voltage                       | V <sub>DD</sub>       |                                         | 1.8  |      | 6.5  | V     |

| V <sub>DD</sub> UVLO Rising                             |                       |                                         |      | 1.6  | 1.8  | V     |

| V <sub>DD</sub> UVLO Hysteresis                         |                       |                                         | 30   | 60   |      | mV    |

| V <sub>BAT</sub> Voltage Rising                         | V <sub>BAT(MIN)</sub> |                                         |      | 1.6  | 1.81 | V     |

| V <sub>BAT</sub> UVLO Hysteresis                        |                       |                                         | 190  | 300  |      | mV    |

| FB Voltage                                              | V <sub>FB</sub>       |                                         | 0.96 | 0.98 | 1    | V     |

| Line Devulation                                         | ΔV <sub>FB</sub>      | 1.8V< V <sub>DD</sub> < 3V              |      |      | 8    | mV    |

| Line Regulation                                         |                       | 3V < V <sub>DD</sub> < 6.5V             |      |      | 7    | mV    |

| Switch-Off Current                                      | IVDD_SW_OFF           | V <sub>FB</sub> = 1.1V                  |      | 1    | 10   | uA    |

| Switch-Off Current                                      | IVBAT_SW_OFF          | V <sub>FB</sub> = 1.1V                  |      | 0.01 | 1    | uA    |

| Shutdown Current<br>I <sub>VDD</sub> +I <sub>VBAT</sub> | I <sub>OFF</sub>      | Charge pin = 0V, V <sub>DD</sub> = 4.5V |      | 0.01 | 1    | uA    |

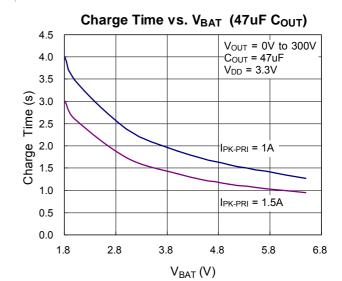

| Minimum Current on Secondary Side                       | IIMCD                 |                                         | 8    | 10   | 12   | mA    |

| EXT On Resistance to V <sub>DD</sub>                    |                       | V <sub>DD</sub> = 3.3V                  |      | 3    | 6    | Ω     |

| EXT On Resistance to GND                                |                       | V <sub>DD</sub> = 3.3V                  |      | 3    | 6    | Ω     |

| STAT On Resistance to GND                               |                       | V <sub>DD</sub> = 3.3V                  |      | 16   | 19   | Ω     |

To be continued

| Parameter                                 | Symbol            | Test Conditions                                                                      | Min  | Тур  | Max  | Units |

|-------------------------------------------|-------------------|--------------------------------------------------------------------------------------|------|------|------|-------|

| Charge Input High Threshold               |                   |                                                                                      |      | 0.7  | 1.3  | V     |

| Charge Input Low Threshold                |                   |                                                                                      | 0.4  | 0.7  |      | V     |

| Minimum Off Time                          |                   | V <sub>BAT</sub> = 1.8V to 6.5V<br>V <sub>DD</sub> = 1.8V to 6.5V                    | 280  | 360  | 430  | ns    |

| IGBT Driver                               |                   |                                                                                      |      |      |      |       |

| IGBT Driver Supply Voltage                | V <sub>VDRV</sub> |                                                                                      | 2.0  |      | 5.5  | V     |

| DRVIN Input High Threshold                |                   |                                                                                      |      | 1.0  | 1.3  | V     |

| DRVIN Input Low Threshold                 |                   |                                                                                      | 0.4  | 1    |      | V     |

| DRVOUT On Resistance to V <sub>VDRV</sub> |                   | V <sub>VDRV</sub> = 3.3V                                                             |      | 6    | 8    | Ω     |

| DRVOUT On Resistance to GND               |                   | V <sub>VDRV</sub> = 3.3V                                                             |      | 6    | 8    | Ω     |

| Propagation Delay (Rising)                |                   | V <sub>BAT</sub> = 1.8V to 6.5V<br>V <sub>DD</sub> = 1.8V to 6.5V                    |      |      | 20   | ns    |

| Propagation Delay (Falling)               |                   | $V_{DD} = 1.37 \text{ to } 0.57$<br>$V_{VDRV} = 2V \text{ to } 6.5V(\text{Note } 3)$ |      |      | 200  | ns    |

| Voltage Detector                          |                   |                                                                                      |      |      |      |       |

| Voltage Detector Trip (Falling)           | V <sub>FBVD</sub> | FBVD Falling                                                                         | 0.96 | 0.99 | 1.02 | V     |

| VDOUT On Resistance to GND                |                   | V <sub>DD</sub> = 3.3V                                                               |      | 16   | 19   | Ω     |

**Note 1.** Stresses listed as the above "Absolute Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may remain possibility to affect device reliability.

Note 2. Devices are ESD sensitive. Handling precaution recommended.

**Note 3.** VDRV is the IGBT gate driving power. Therefore, setting VDRV voltage must consider IGBT gate threshold voltage, and its driving capability.

90

350

340

330

320

310 300

290

280 270

260 250

Output Voltage (V)

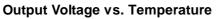

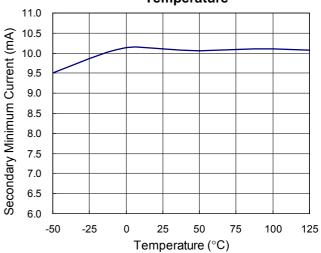

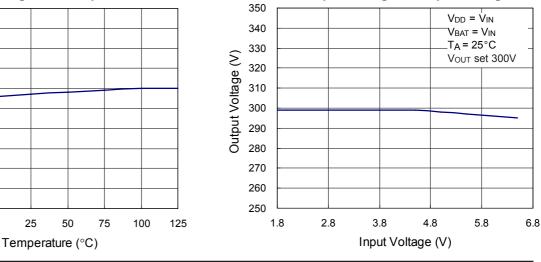

## **Typical Operating Characteristics**

Secondary Minimum Current vs. Temperature

Output Voltage vs. Input Voltage

Patent Pending

-50

-25

0

25

50

# Richtek

## **Application Information**

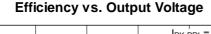

The RT9591 integrates a constant peak current controller for charging photoflash capacitor, an IGBT driver for igniting flash tube, and a voltage detector with open drain output to provide a cost effective photoflash solution.

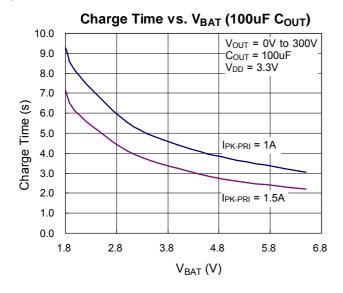

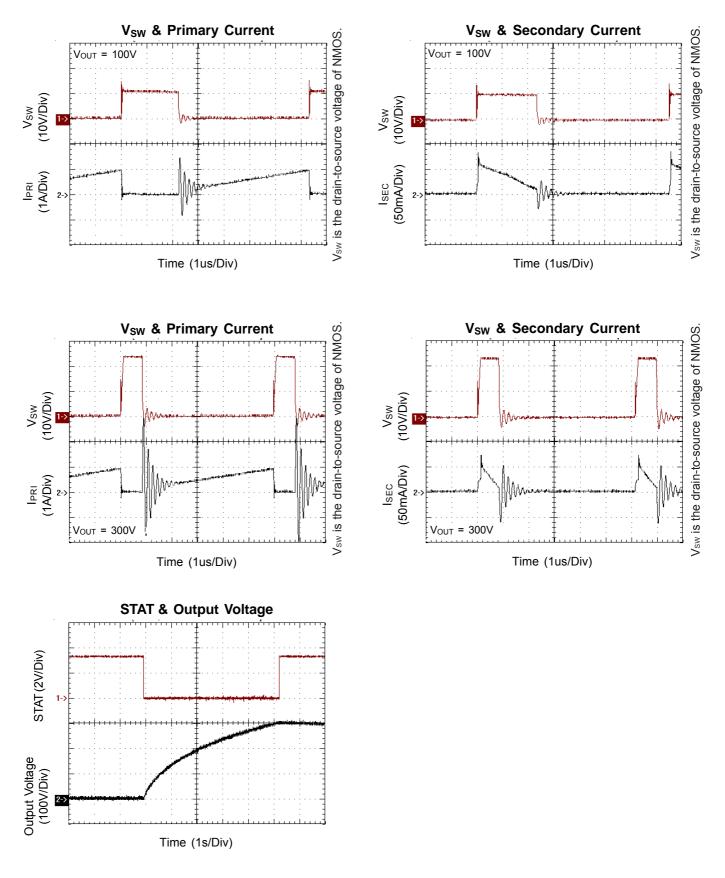

The photoflash capacitor charger uses constant primary peak current and constant secondary valley current control to efficiently charge the photoflash capacitor. Pulling the CHARGE pin high initiates the charging cycle. During ON time, the primary current ramps up linearly according to  $V_{BAT}$  and primary inductance. A resistor connecting to CS pin determines the ON time of primary NMOS and consequently the primary peak current.

During the OFF time, the energy stored in the flyback transformer is boosted to the output capacitor. The secondary current decreases linearly at a rate determined by the secondary inductance and the output voltage (neglecting the voltage drop of the diode). The secondary current is monitored by the IMCD pin. When the secondary current drops below 10mA, ON time starts again. The charging cycle repeats itself and charges the output voltage.

The output voltage is sensed by a voltage divider connecting to the anode of the rectifying diode. When the output voltage reaches the desired voltage set by resistor divider, the HV detector will terminate the charging cycle, disable the charging block and pull high the STAT pin. The voltage sensing path is cut off when charging completed to minimize the output voltage decay. Both the CHARGE and STAT pins can be easily interfaced to a microprocessor in a digital system.

#### Transformer

The flyback transformer should be appropriately designed to ensure effective and efficient operation.

#### 1. Turns Ratio

The turns ratio of transformer (N) should be high enough so that the absolute maximum voltage rating for the NMOS drain to source voltage is not exceeded. Choose the minimum turns ratio according to the following formula:

$N(\text{MIN}) \geq \frac{V \text{OUT}}{V \text{DS}(\text{MAX}) - V \text{BAT}}$

V<sub>OUT</sub>: Target Output Voltage

V<sub>DS(MAX)</sub>: Maximum drain to source voltage of NMOS

#### 2. Primary Inductance

Each switching cycle, energy transferred to the output capacitor is proportional to the primary inductance for a constant primary current. The higher the primary inductance is, the higher the charging efficiency will be. Besides, the RT9591 has a 360ns minimum-off time for correct current and voltage sensing. To ensure the charger operating in continuous conduction mode, the primary inductance should be high enough according to the following formula:

$L\mathsf{PRI} \geq \frac{430 \text{ x } 10^{-9} \text{ VOUT}}{N \text{ x } \mathsf{IPK} - \mathsf{PRI}}$

V<sub>OUT</sub>: Target Output Voltage

N : Transformer turns ratio

IPK-PRI : Primary peak current

$430 \times 10^{-9}$ : The maximum value of minimum-off time.

#### 3. Leakage Inductance and Parasitic Capacitance

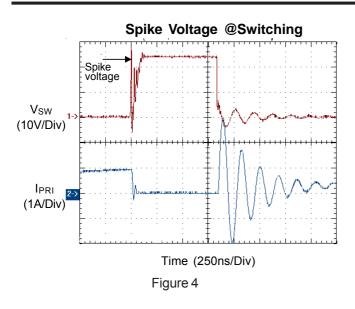

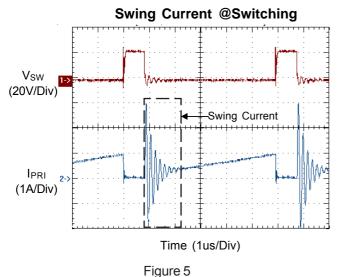

The leakage inductance of the transformer results in the first spike voltage when NMOS turns off as shown in Figure 4. The spike voltage is proportional to the leakage inductance. The spike voltage must not exceed the dynamic rating of the NMOS drain to source voltage. Well-coupling winding design decreases the leakage inductance. However, well-coupling winding design usually results in large parasitic capacitance between windings. The parasitic capacitance consequently causes initial current swing when NMOS turns on as shown in Figure 5. Trade off is necessary between leakage inductance and parasitic capacitance.

#### 4. Transformer Secondary Capacitance

Any capacitance on the secondary can severely affect the efficiency. A small secondary capacitance is multiplied by  $N^2$  when reflected to the primary side. This capacitance forms a resonant circuit with the primary leakage inductance of the transformer. Therefore, both the primary leakage inductance and secondary side capacitance should be minimized.

#### **Rectifying Diode**

The rectifying diode should be with short reverse recovery time (small parasitic capacitance). Large parasitic capacitance increases switching loss and lowers charging efficiency. In addition, the peak reverse voltage and peak current of the diode should be sufficient. The peak reverse voltage of the diode is approximately:

$V_{PK-R} \approx V_{OUT} + (N \times V_{BAT})$

The peak current of the diode equals primary peak current divide transformer turn ratio as the following equation:

$I_{PK-SEC} = I_{PK-PRI}/N$

Note: N is transformer turns ratio.

#### NMOS

The NMOS is the switching component of the flyback converter. Select adequate drain to source voltage and NMOS turn ON drain current is very important. For the RT9591 typical application circuit,

If  $V_{OUT}$  = 300V,  $V_{BAT}$  = 6.5V, transformer turn ratio N = 15.

$V_{DS(MIN)} = 300/15 + 6.5 = 26.5V.$

The NMOS minimum drain to source voltage should be greater than 26.5V.

In addition, make sure that  $V_{\text{DD}}$  is higher than  $V_{\text{GS(th)}}$  (Gate threshold voltage) so as to sufficiently turn on the MOSFET.

#### Capacitor

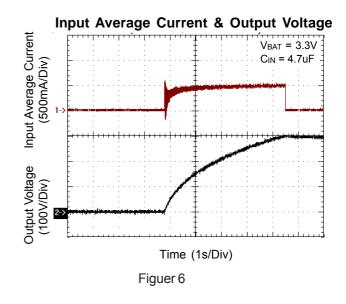

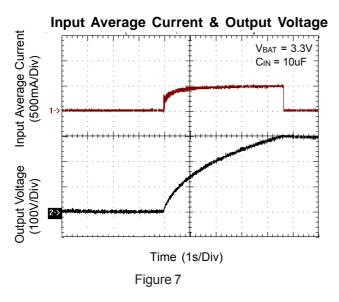

X5R ceramic capacitor  $\ge 10 \text{uF}/10\text{V}$  is recommended for input capacitor to well decouple the switching current. Figure 6 and Figure 7 compare the input current waveforms with different input capacitors.

# Richtek

#### **Adjustable Input Current**

The RT9591 simply adjusts peak primary current by a resistor  $R_{CS}$  connecting to CS pin as shown in Function Block Diagram.  $R_{CS}$  paralleled with internal 1M $\Omega$  resistor determines the ON time of primary NMOS.

During the ON time, the primary current ramps linearly with a slope =  $V_{BAT}/L_{PRI}$ . Consequently, the current setting resister (R<sub>CS</sub>) could be calculated as:

Ra =

$$\frac{(I_{PK} - PRI - 8 \times 10^{-3} \times N) \times L_{PRI}}{30 \times 10^{-12}}$$

Rcs =  $\frac{1M \times Ra}{1M - Ra}$  (Ω)

Where  $I_{\mathsf{PK}\text{-}\mathsf{PRI}}$  is the primary peak current and N is the turns ratio of transformer.

Users could select appropriate  $R_{CS}$  according to the battery capability and required charging time.

#### Minimum I<sub>PK-PRI</sub> Limitation

$$The \, \mathsf{I}_{\mathsf{PK}} \, \cdot \, \mathsf{PRI} \, setting \, must \ \geq \frac{430 \, x \, 10^{-9} \, x \, \mathsf{V}_{\mathsf{OUT}}}{\mathsf{N} \, x \, \mathsf{L}_{\mathsf{PRI}}} \, ,$$

where 430 x  $10^{-9}$  is the maximum value of minimum off time.

If lower  $I_{PK-PRI}$  setting limitation is required, you may change transformer to incease N x  $L_{PRI}$  product.

#### Adjustable Output Voltage

The RT9591 senses output voltage by a voltage divider connecting to the anode of the rectifying diode during OFF time. This eliminates power loss at voltage-sensing circuit when charging completed. R3 to (R1+R2) ratio determines the output voltage as shown in the application circuit Figure 1. The feedback reference voltage is 0.98V. If  $V_{OUT}$  = 300V, in Figure 1 Photoflash Capacitor Charger Application according to the following equation:

Vout = VFB×(1+

$$\frac{R1+R2}{R3}$$

), so  $\frac{R1+R2}{R3}$  = 305

R3 is recommend 1K $\Omega$ ; R1 and R2 are used 150K $\Omega$  for reducing parasitic capacitance coupling effect of FB pin. R1 and R2 **MUST** be greater than 0805 size resister for enduring secondary HV.

#### Lower Charging Current at Low Battery Voltage

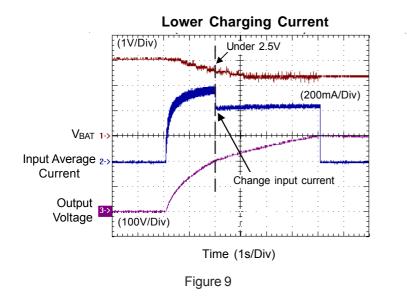

The RT9591 integrates a voltage detector with open drain output. This voltage detector is specially designed for lowering peak primary current and minimizing the impact to battery voltage at low V<sub>BAT</sub> condition as shown in Figure 8. The voltage detector senses V<sub>BAT</sub> through a resister divider R6 and R7 and compares it with internal 1V reference voltage. When the sensed voltage is lower than the reference voltage, VDOUT pin goes low and changes the resistance connecting to CS pin and the ON time. For example, if R6 equal 1.5M $\Omega$  and R7 equal 1M $\Omega$ , VDOUT pin change status form open to ground when V<sub>BAT</sub> voltage under 2.5V. And current setting resister R4 and R5 can set different resistance for different input current when V<sub>BAT</sub> voltage under detector voltage. Figure 9 shows the lower charging current waveform. When V<sub>BAT</sub> voltage under 2.5V, the input average current become approximately 600mA to 460mA.

Figure 8. Lower charging current application circuit

Figure 10. IGBT driver input signal

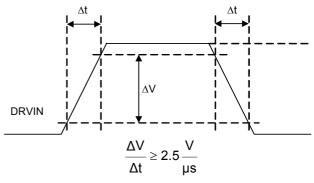

#### **IGBT Driver Input Signal**

The slew rate of IGBT driver input DRVIN should be higher than  $2.5V/\mu s$  for normally triggering the IGBT as shown in Figure 10.

#### Layout Guide

1.Both of primary and the secondary power paths should be as short as possible.

- 2.Keep FB node area small and far away from nodes with voltage switching to reduce parasitic capacitance coupling effect.

- 3. The NMOS ground and feedback ground should be connect to V<sub>BAT</sub> ground for reduce switching noise.

# **Outline Dimension**

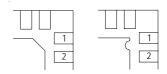

DETAIL A Pin #1 ID and Tie Bar Mark Options

Note : The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

| Symbol | Dimensions | n Millimeters | Dimensions In Inches |       |  |

|--------|------------|---------------|----------------------|-------|--|

| Symbol | Min        | Max           | Min                  | Max   |  |

| A      | 0.800      | 1.000         | 0.031                | 0.039 |  |

| A1     | 0.000      | 0.050         | 0.000                | 0.002 |  |

| A3     | 0.175      | 0.250         | 0.007                | 0.010 |  |

| b      | 0.180      | 0.300         | 0.007                | 0.012 |  |

| D      | 2.950      | 3.050         | 0.116                | 0.120 |  |

| D2     | 1.300      | 1.750         | 0.051                | 0.069 |  |

| E      | 2.950      | 3.050         | 0.116                | 0.120 |  |

| E2     | 1.300      | 1.750         | 0.051                | 0.069 |  |

| е      | 0.500      |               | 0.0                  | )20   |  |

| L      | 0.350      | 0.450         | 0.014                | 0.018 |  |

V-Type 16L QFN 3x3 Package

#### RICHTEK TECHNOLOGY CORP.

Headquarter

5F, No. 20, Taiyuen Street, Chupei City Hsinchu, Taiwan, R.O.C. Tel: (8863)5526789 Fax: (8863)5526611

#### RICHTEK TECHNOLOGY CORP.

Taipei Office (Marketing) 8F-1, No. 137, Lane 235, Paochiao Road, Hsintien City Taipei County, Taiwan, R.O.C. Tel: (8862)89191466 Fax: (8862)89191465 Email: marketing@richtek.com